# **Electronic Interfaces for Optical Packet Switching and Routing**

D. Maia Jr<sup>2</sup>, L. Pezzolo<sup>1</sup>, Edson Moschim<sup>2</sup>, F. Rudge Barbosa<sup>1</sup>

<sup>1</sup>Fundação CPqD, Campinas – SP, 13088-902, Brasil <sup>2</sup>State University of Campinas, Campinas SP, 13083-970, Brasil

Resumo – Apresentam-se aqui novos circuitos para identificação, roteamento e resolução de contenda entre pacotes ópticos com cabeçalho em freqüência, integralmente desenvolvidos em nossos laboratórios. Os tempos de processamento dos circuitos eletrônicos são muito rápidos: os circuitos de reconhecimento de cabeçalho (HRC) e de decisão lógica (LDC) respondem em 40 ns. Ambos circuitos foram construídos usando tecnologia fast TTL. O chaveamento, roteamento e a solução de contenda são realizados pacote-a-pacote sem que haja degradação ou perda de pacotes ópticos. Este sistema é aplicável em chaveamento óptico de pacotes em futuras redes fotonicas transparentes.

*Palavras Chave* - Chaveamento óptico, eletrônica de alta velocidade e redes ópticas de pacotes.

Abstract – Novel electronic circuits have been developed in our labs to identify, route and solve contention between optical packets having frequency tone header. The detection and processing times of the electronic circuits are very short: the header recognition circuit (HRC) and the logical decision circuit (LDC) response times are both 40 ns. The circuits use fast TTL technology. The switching, routing and contention solution is performed on a packet-by-packet basis, without degradation or loss of packets. This system is applicable to future photonic network.

*Key-words* – Photonic switching, fast electronic and optical packet networks.

# I. INTRODUCTION

Technology of optical packet is being extensively researched to be applied in optical next generation networks (ONGN) [1,2]. By using optical packets in the optical network, following the 'connectionless' principles of IP packets, optical packet switching naturally comes into scene. This technology offers decentralized switching and routing and high-capacity connections to end-users.

This work focuses on optical packet switching technology [3,4], and its enabling technologies. The optical packets here are formed by an RF frequency header and high-capacity digital payload. The header contains the address information and the digital payload contains the end user information, and is transparent to data rate and format. Here we describe a new system to identify and route these optical packets, consisting of a fast TTL logic [5] circuits that will act on the optical switch to route optical packets in the optical node. The header recognition circuit (HRC) identifies the header of optical packets, which is a frequency tone in the low RF range; this tone corresponds to the node address of the optical packet, according to pre-established allocation table, which relates the incoming packet to a preferred output port. The logical decision circuit (LDC) receives the gating signal proceeding from the HRC, processes the information and delivers it as a signal to acousto-optical (AO) switch that will keep or change state to correctly routing.

### **II. PACKET STRUCTURE AND GENERATION**

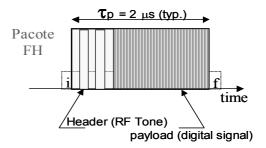

In Fig. 1 we can see the structure of the optical packet that will be recognized and routed by the electronic circuits. The optical packets have duration  $2\mu$ s, with 25-75% ratio for header and payload fields, but other durations and ratios are possible. Address and payload thus form a TDD (time division duplexing) structure.

Fig. 1 – Structure of optical Packet FH

The packets are constructed directly in the pattern generator; the header is compound by transitions enter bits 1's and 0's; and the payload is constructed by a PRBS  $(2^{23} - 1)$ , each in a separate field with predefined number of bits. Address information is provided by the header tone frequency, which is effectively the rate of transitions between low and high level thresholds within the header, or in the interval between subsequent transitions. Therefore, the headers are constructed by an alternated sequence of bits 0's and 1's within the header time interval. At the moment, we are working with three header frequencies, respectively 3.8, 6.3 and 8.9 MHz. The field of header is compound by 1260 bits, the payload by 3780 bits and the separation between the packets by 2520 bits. The three effective header frequencies have the same number of bits and size.

#### **III. HEADER RECOGNITION CIRCUIT (HRC)**

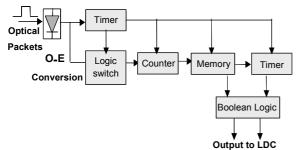

As stated previously, each packet address is uniquely determined by the frequency of the tone contained in its header. The optical packets arrive in the HRC after the opto-electrical conversion. Therefore, the process to identify the header is a frequency measuring. However, the speed of address identification is a crucial issue, as it directly impacts on the switching process speed and, consequently, on the latency of the network. With the HRC we obtain a processing time of 450 ns, with the use of fast TTL (74 series) circuit technology. However, signals analysis shows that RF pulses spectral components may mislead precise detection of the tone. To overcome this, we used the basic counter principle. The Fig. 2 shows the functional block diagram of this circuit.

Fig. 2 - Functional block diagram of the switch control circuit

The first timer is triggered by the rising edge of an incoming packet entering the node and controls a logic switch. Gating is fixed and equal to the header duration. Each rising transition within gating times adds 1 to an initial reset counter. At the end of the gating period (header), counting is transferred to a simple memory the counter and the first timer are reset, becoming available for the next count. The first timer acts the second timer, and your function is open a gating time with duration equal and fixed to the packet size. Important to point out is that level transitions within the body (digital payload) signal do not trigger the timers or the counter as long as the ratio between the bit rate and maximum sequence length of equal symbols (1's or 0's) is held than 400 MHz, due to the limitation in the logic switching speed (200MHz).

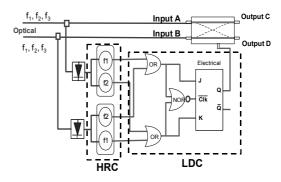

In Fig. 3 one can see the gating opened by circuit of header recognition, that will be delivered to the LDC.

Fig. 3 - Gates of Circuit Header Recognition

This gate is referent to output of header recognition that delivers these signals to LDC. The upper trace corresponds at the  $f_1$  and the lower traces  $f_2$ . The length of this gate is 3.0µs, and it will delivered to the LDC, that after process these information, it will make that the switch keeps or changes your current state. The gating length corresponds to the minimum time that the switch will keep your current state, parallel or crossed, and this time must be bigger that packet time, looking for integrity of all packets in the network.

#### **IV. LOGICAL DECISION CIRCUIT (LDC)**

The LDC is implemented to solve contention between packets arriving to the node within the same packet time, and having the same frequency header (same address); this also eliminates packet loss. The optical hardware is the sane already implemented to work with the signal deriving from HRC, as depicted in Fig. 4. The LDC uses Boolean logic to process the information and delivers a TTL signal to act the AO switch.

*Fig.* 4 – *Experimental set-up for Optical Packet Switching node, with contention resolution.*

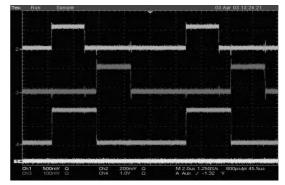

In Fig. 5, we see the gates referents to packets with header  $f_1$  deriving from the header recognition circuit and the result that will make the AO switch changes your state. This situation presents the condition of packets routing to the same output, and not contention between optical packets.

Fig. 5 – Actuation of LDC on the AO switch

The LDC is receiving gates corresponding to packets with header  $f_1$ , and since we are routing only packets with this frequency, both packets  $f_1$  requires the same output. We can see that the optical packets arrive at different time intervals. The top trace is the gate correspondent to packets passing through the

channel that arrives in the input A of the AO switch, and the middle trace are packets arriving at input B. The bottom trace represents the response of LDC that will make the AO switch change your state. In the moment that arrives the first packet in the input A, the circuit assumes a high logic level and make the switch assumes a parallel state to transfer it to the output C. The LDC make the AO switch keeps your state until all packet information is transferred and until a new event occurs, that is, arrives another packet at input B, fact that guarantee the integrity of all packets.

When the packet arrives at the input B, the LDC sends a low logic level to AO switch, making it change your actual state. After the switch assumes the crossed state, the packet information is transferred to the output C. This proceeding is continuous and, as stated, supplies the conditions of switching and routing.

When two packets with same header, arrives at the same packet time at the inputs of AO switch, situation that presents contention between optical packets, and requires the same output, the LDC analyze that packet arrive first and directed it to the preferential output, while another packet is transferred to the nonpreferential output (deflection routing). Then this packet will go through few more hops in the network, until your correct routing in the next nodes. The LDC provides the integrity of packet too. When a packet is being routed and arrives another one requiring the same output, the LDC cannot stop this transmission to serve this requisition, because it would occur loss of packets. When a packet is passing through the AO switch, the LDC blocks the switch in current state to prevent packet loss.

# V. CONCLUSION

We have designed and demonstrated the operation and applicability of the header recognition circuit (HRC) and the logical decision (LDC) for optical packet networks. With these circuits operating together, we obtain an excellent performance of header detection and correct switching and routing of optical packets with header in frequency domain. This circuit provides fast processing of information, around 0.45  $\mu$ s to header recognition and 0.1  $\mu$ s for the LDC. Using this circuit, we obtain single packet switching and solve the contention between packets in various situations of packet traffic, keeping packet integrity.

#### References

- 1) D. Chiaroni, "Status and Applications of Optical Packets Switching", paper WeM1, *ECOC'2001*, Amsterdam, September 2001.

- 2) D. J. Blumenthal, "Photonic Packet and All-Optical Label Switching Techniques and Technologies", paper WO3, *OFC'2002*, Anaheim, USA, March 2002.

- F. R. Barbosa, D. Maia Jr, E. Moschim, L. Pezzolo, A. C. Sachs, "Optical Packet Switching System for Optical Nodes in Next-Generation

Metropolitan and Access Networks", to be published in *Rev. INATEL, no.2, 2003.*

- 4) F. Rudge Barbosa, Décio Maia, L. Pezzolo, A. C. Sachs, M.R.Salvador, "Optical Packet Switching Node for Metro-Access Networks", paper We4.P-160, Proceed. 29th. European Conference on Optical Communications ECOC'2003, Rimini, Itália, Sept. 2003

- 5) Data Handbook Fast TTL Logic Series Philips, 2001

## **ABOUT THE AUTHORS**

Décio Maia Junior was born in Minas Gerais, Brazil, 1978. on October 03. He gratuated as Telecommunications Engineer from Instituto Nacional de Telecomunicações (INATEL) at Santa Rita do Sapucaí, Brazil, in 2001. Actually he is master degree student at Universidade Estadual de Campinas (UNICAMP) in Department of Semiconductors, Instrumentations and Photonics (DSIF) and theme thesis is Transport Systems based on Optical Packet Switching (OPS), developed on department of optical communications at Fundação CPqD.

**Leonardo Pezzolo** was born in São Paulo, Brazil, on November 06, 1956. He gratuated as Telecommunications Engineer from Escola Politécnica da Universidade de São Paulo (USP) at São Paulo, Brazil, in 1979. He is currently working for the Department of Optical Communications at Fundação CPqD.

Felipe Rudge Barbosa - has a bachelor degree in Physics, from PUC-RJ; a Master's degree in Physics, from IFGW-UNICAMP; and a Ph.D. in electrical engineering, from FEEC-UNICAMP. He is presently technical consultant and senior researcher at Fundaçao CPqD. He has been active in research and development, and technology transfer in Optical Communications for many years, with activities ranging from fiber technology and opto-electronic devices, including optoelectronic packaging, to optical systems and photonic networks. In recent years he has been project leader in Optical Access Networks. Dr. Rudge has several publications and presentations in international journals and conferences. He is also active as instructor and speaker in those fields, having participated of various events at INATEL. He is Member of SBrT, SBMO, SBF and the Optical Society of America (OSA).

Edson Moschim was born in São Paulo, Brazil. He received the M.S. degree in electrical engineering from the State University of Campinas (UNICAMP), São Paulo, Brazil, in 1983, and the Ph.D. degree in applied physics in 1989 from the University of Paris-Sud, Orsay, France. From 1978 to 1985 he worked with CPqD/Telebrás, Campinas, with optical fiber communications systems. Since 1985, he has been a staff member of the School of Electrical and Computer Engineering at UNICAMP, where he is now a Professor and researcher interested in photonic technology, electromagnetism, and software for systems simulation